Para surfar a onda da IA, Samsung promete aos clientes fábrica de chips 20% mais rápida

Empresa sul-coreana reformolou os processos produtivos para reduzir tempo de fabricação de processadores e outros componentes usados para inteligência artificial

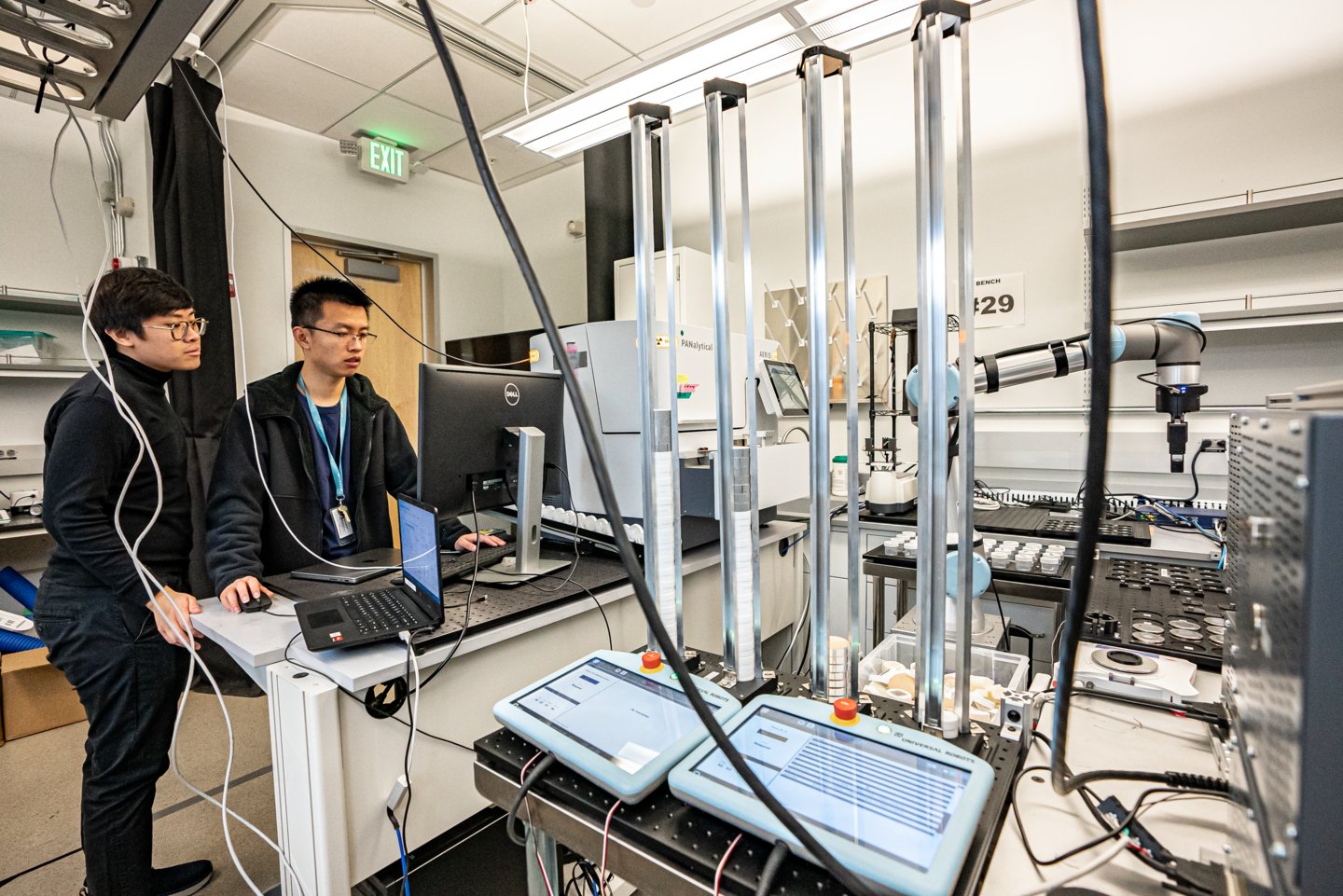

Siyoung Choi: presidente e gerente geral da Foundry Business da Samsung (Samsung/Divulgação)

Repórter

Publicado em 13 de junho de 2024 às 14h54.

Última atualização em 13 de junho de 2024 às 14h55.

A Samsung anunciou que seu negócio de manufatura por contrato oferecerá um serviço completo para a produção de chips de IA, integrando suas áreas de chips de memória, fundição e embalagem. A empresa visa aproveitar o crescimento do mercado de IA ao reduzir o tempo de produção dos chips em aproximadamente 20%.

Durante um evento em San Jose, Califórnia, Siyoung Choi, presidente e gerente geral da Foundry Business da Samsung, destacou a transformação trazida pela IA generativa no cenário tecnológico. Choi prevê que a receita global da indústria de chips crescerá para US$ 778 bilhões até 2028, impulsionada pela demanda por chips de IA.

Amazon enfrenta desafios para integrar IA generativa na Alexa, revelam ex-funcionáriosEm uma coletiva de imprensa antes do evento, Marco Chisari, vice-presidente executivo de vendas e marketing da Foundry, afirmou que as projeções de alta demanda por chips de IA feitas por Sam Altman, CEO da OpenAI, são realistas. Altman informou à TSMC que deseja construir cerca de três dezenas de novas fábricas de chips.

A Samsung é uma das poucas empresas que combina venda de chips de memória, serviços de fundição e design de chips em um só lugar. Apesar de, no passado, essa combinação ter gerado receios entre clientes sobre possíveis vantagens competitivas para a Samsung, a crescente demanda por chips de IA e a necessidade de integração de componentes tornaram essa abordagem uma vantagem.

A Samsung também destacou sua arquitetura de chip de ponta conhecida como gate all-around (GAA), que melhora o desempenho dos chips e reduz o consumo de energia. A empresa planeja produzir em massa sua segunda geração de chips de 3 nanômetros usando GAA no segundo semestre deste ano.

Além disso, a Samsung anunciou seu mais recente processo de fabricação de chips de 2 nanômetros para computação de alto desempenho, que posiciona trilhos de energia na parte traseira do wafer para melhorar a entrega de energia. A produção em massa está prevista para 2027.

:format(webp))